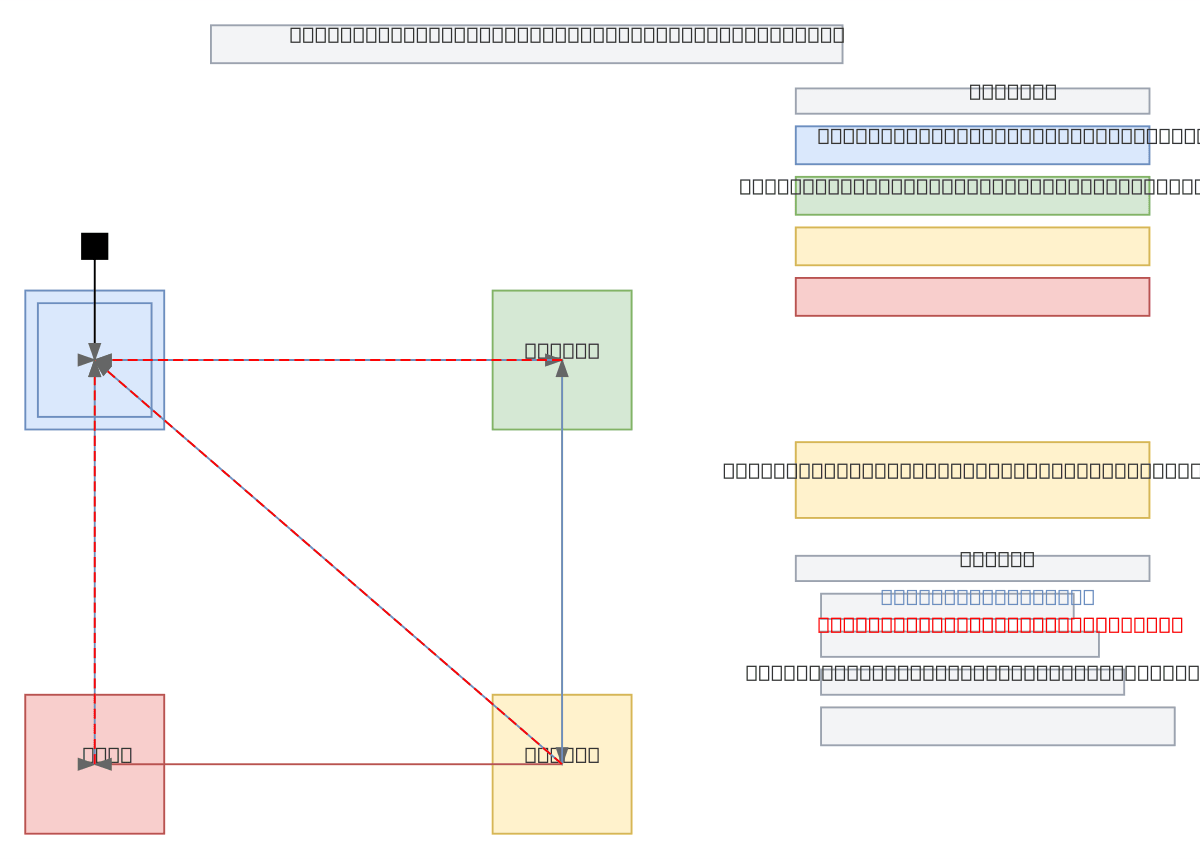

Button Press Detector FSM

About This Architecture

Finite state machine for debounced button press detection with five states: IDLE, COUNT1, COUNT2, LONG, and asynchronous RESET. The FSM transitions through counting states as the button remains pressed, distinguishing between short presses (COUNT1/COUNT2) and long presses (LONG ≥3 cycles). RESET forces immediate return to IDLE from any state, enabling responsive interrupt handling. This pattern eliminates switch bounce noise and provides clean output symbols for downstream logic. Fork this diagram on Diagrams.so to customize state names, timing thresholds, or output signal definitions for your specific application. The double-circle initial state notation and dashed RESET transitions follow standard FSM conventions for clarity in hardware design documentation.

People also ask

How do you design a finite state machine to debounce button input and detect short vs. long presses?

This FSM uses five states to debounce button input: IDLE waits for a press, COUNT1 and COUNT2 track consecutive clock cycles of button activity, and LONG detects presses ≥3 cycles. An asynchronous RESET forces return to IDLE from any state, enabling interrupt-driven cancellation. Output symbols and valid flags mark state transitions for downstream logic.

- Domain:

- Electrical Engineering

- Audience:

- Digital logic designers and embedded systems engineers implementing debounced button input handling

Generated by Diagrams.so — AI architecture diagram generator with native Draw.io output. Fork this diagram, remix it, or download as .drawio, PNG, or SVG.